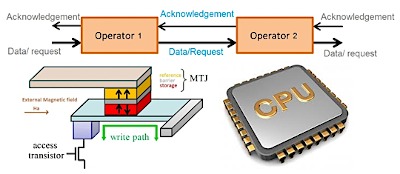

NV-APROC stands for Non Volatile MRAM-based Asynchronous PROCessor, a 42-month ANR project starting on October 2019, coordinated by Spintec. Micro and nano electronics integrated circuit domain has been strongly driven by the advent of the Internet of Things (IoT). The constraints become very strong, especially in terms of power consumption and autonomy. Therefore there is an important need to propose new efficient solutions.

NV-APROC main goal is to significantly decrease the power consumption of processors compared to conventional volatile systems, by proposing a novel hybrid clock-less non-volatile architecture. The targeted circuit will use the so-called asynchronous design technique, which is already well known to be energy efficient, and MRAM emerging non-volatile technology (peSTT and SOT) which has a really interesting set of features in terms of write / read energy and CMOS process integration and compatibility. In order to demonstrate the potential of such an approach, we propose to benchmark our innovative work up to full layout with state of the art synchronous version of the processor. By the end of the project we will highlight a complete study of several architectures providing the best way to go forward in a real breakthrough for ultra-low power applications.

More information

- Contact: Grégory Di Pendina, from the Spintronic IC Design team.

- Web site of NV-APROC.

Publications

[ At Spintec (default) | Entire consortium ]