Overview

The team is dedicated to the evaluation of the benefits of using magnetic devices in Integrated Circuits (ICs). It is expected that integrating non-volatility in ICs could contribute to push forward the incoming limits in the microelectronics scaling. This work includes integrating the magnetic devices in standard design tools, design hybrid circuits and evaluate their performance for various applications. The unique combination of advantages of spintronics devices (non-volatility associated with high speed and endurance, analogue capabilities, well controlled stochastic behavior…) allows intrinsically mixing the memory and logic functionalities (in Memory Computing). This opens the way towards new computing paradigms, beyond the standard Von-Newman architecture of computing systems. The most interesting applications addressed in the team are described below.

Research topics

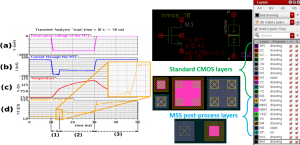

Hybrid CMOS/Magnetic design flow

Designing hybrid circuits requires integrating the magnetic devices in the standard design flow of microelectronics. This includes compacts models for electrical simulations, technology files including the magnetic back-end and libraries of Standard Cells for digital design.

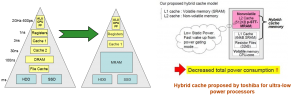

Low-power logic circuits

One issue related to microelectronics scaling is the increasing standby power, due to leakage currents. Introducing non-volatility in circuits allows easing the power gating technique, which consists in cutting-off the power supply of inactive blocks to save leakage.

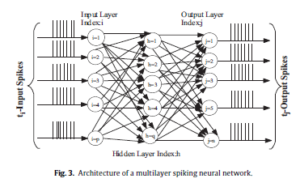

Artificial intelligence

Spiking Neural Networks are seen as a Key building block for strongly improving the energy efficiency of current AI applications and opening up new possibilities (in terms of unsupervised learning, recurrent networks, probabilistic inference, etc.). The scientific challenges to be tackled are the following: the first one is to define power-constrained learning and inference algorithms (online, supervised, unsupervised, probabilistic, etc.). The second one is to design a scalable and flexible SNN architecture, adaptable to the different above-mentioned algorithms, and fabricate that circuit in hybrid nanoscale CMOS and NVM technology, enabling very dense synaptic density. The last objective is to derive a principled toolchain for the algorithm, design, development, and integration of spiking neural networks for future adoption in industrial health and automotive embedded applications.

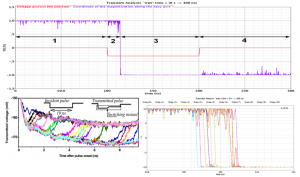

IC Reliability : Hardware security

While STT MRAM can be beneficial for hardware security (taking advantage of its stochastic behavior for cryptography for instance), it also presents some specific failures mechanisms that has to be studied to take the appropriate countermeasures.

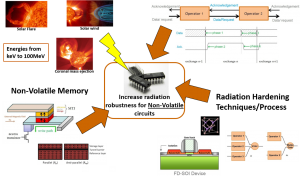

IC Reliability : Radiation hardening

The intrinsic hardness to radiations of the magnetic devices make them a good candidate to be embedded in circuits for space applications. It can be advantageously combined with other hardening technologies or design techniques targeting space applications.

The team

Projects

Present

- SCREAM, ANR (2025-2028) – Secure Processor with MRAM Technology

- SPINFROST, ANR (2023-2026) – Design of ferroelectric spintronic architectures for ultra-low power memories, post-CMOS logic and neuromorphic computing

- QUALMEM, ANR (2023-2026) – Quality Assurance of Advanced and Emerging Memory Technologies by Using Machine Learning

- PEPR-ELEC, ANR (2022-2027) – Programmes et Equipements Prioritaires de Recherche Electronique

- MAD300, CEA internal (2023 – 2027) – Memory Advanced Demonstrator

Former members

Permanent Staff

- Christophe LAYER : Research scientist

- François DUHEM: Research scientist

Post-docs

- Chadi AL KHATIB (2021-2023)

- Pablo ILHA VAZ (2022-2022)

- Ghislain TAKAM TCHENDJOU (2020-2021)

- Pierre VANHAUWAERT (2014-2017)

- Eldar ZIANBETOV (2014-2017)

- Kotb JABEUR (2013-2017)

- Virgile JAVERLIAC (2013-2014)

- Fabrice BERNARD-GRANGER (2013-2014)

- Yun YANG (2012-2013)

- Abdelilah MEJDOUBI (2010-2012)

PhD

- Yacine MEHADJI (supervised by L. Anghel and G. Prenat) (2024)

- Kamal DANOUCHI (supervised by L. Anghel and G. Prenat) (2021-2024)

- Odilia COI (supervised by G. Di Pendina, D. Dangla and L. Torres) (2018-2021)

- Antoine HERAUD (supervised by L. Anghel and Alexandre Valentian) (2020-2022)

- Etienne BECLE (supervised by L. Anghel , G. Prenat and I.L. Prejbeanu) (2019-2021)

- Mounia KHARBOUCHE (supervised by G. Di Pendina, R. Wacquez and J.M. Portal) (2016-2019)

- Rana ALHALABI (supervised by G. Di Pendina, E. Nowak and L. Prejbeanu) (2016-2019)

- Jeremy LOPES (supervised by G. Di Pendina, E. Beigne, D. Dangla and L. Torres) (2014-2017)

- Erya DENG (supervised by G. Prenat and L. Anghel) (2014-2017)

- Olivier GONCALVES (supervised by G. Prenat and B. Dieny) (2009-2012)

- Wei GUO (supervised by G. Prenat and B. Dieny) (2006 – 2010)

- Mourad El BARAJI (supervised by G. Prenat and B. Dieny) (2007-2009)

Engineers

- Stephane GROS (2013-2014)

- Pierre PAOLI (2013-2014)

Former projects

- CARMEM, 80|PRIME – CNRS (2021-2024) – Modèles de Caractérisation par Apprentissage pour la Qualité des Technologies de Mémoires Émergentes

- NEUSPIN, ANR/DFG (2021-2024), Design of a reliable edge neuromorphic system based on spintronics for Green AI

- MISTRAL, ANR (2019-2024) – MRAM/CMOS Hybridization to secure cryptographic algorithms

- NV-APROC, ANR (2019-2023) – MRAM-based Non-volatile Asynchronous Processor

- SPINBRAIN (2020-2022) – Spintronic-based Neural Network

- HANS, UGA (2019-2022)

- GREAT, H2020 (2016-2019)

- MASTA, ANR (2016-2019)

- ELECSPIN, ANR (2016-2020) – Electric-filed control of spin-based phenomena

- NOVELASIC, CEA-nanosciences (2015)

- MAD200, CEA internal (2014-2018) – Memory Advanced Demonstrator

- SPOT, H2020 (2012-2015)

- MARS, ANR (2012-2015)

- DIPMEM, ANR (2012-2015)

- HYMAGINE, ERC Advanced grant (2010-2015)

Partners

- NanoXplore

- LIRMM

- IM2NP

- TIMA

- University of Montpellier

- KIT

- NanoXplore

- TRAD

- TUD

- University of Brasov

- CEA-LETI

- CEA-LIST

- Nellow

- IEF – C2N

- University of Aix-Marseille

- CEA Tech (Gardanne)

- EMSE (Gardanne)

- Greenwaves

- eVaderis

- TowerJazz

- Singulus

- Toplink Innovation

- Tiempo Secure

- Starchip

- CNES

- Dolphin Integration

- SIGFOX

- Antaios

- IHP

- Thales TRT

- University of Newcastle

- EM Marin

Recent news

- Post-Doctoral position – FPGA-based and ASIC-based system level processor architecture development (July 01st, 2025)

POST DOC Recruitment on FPGA-based and ASIC-based system level processor architecture development Context: The last decade has seen the emergence of numerous studies around integrated nanoelectronic technologies for a growing number of application areas, ranging from the ... - PhD offer – PRObabilistic on-edge learning for SPINtronic-based neuromorphic systems (May 13th, 2025)

Thesis topic PRObablistic on-edge learning for SPINtronic-based neuromorphic systems Job description The hired joint UGA – KIT PHD candidate should be able to cover the work of the workpackage 1 and 2. He/she will also participate to technical ... - seminar – Energy and computing : Identifying and addressing bottlenecks (October 07th, 2024)

On Friday October 18th 2024, Jonathan MIQUEL (SPINTEC) will give us a seminar at 11:00 entitled : Energy and computing : Identifying and addressing bottlenecks Place : IRIG/SPINTEC, auditorium 445 CEA Building 10.05 (access to CEA requires ... - Resistively-coupled stochastic MTJ for energy-based optimum search (January 22nd, 2024)

We study recurrent networks of binary stochastic Magnetic Tunnel Junctions (sMTJ), aiming at efficiently solving computationally hard optimization problems. After validating a prototyping route, we investigate the impact of hybrid CMOS+MTJ building block variants on ... - [Filled] Associate Professor position – Digital and mixed level circuit and architecture design and validation (December 08th, 2023)

![[Filled] Associate Professor position - Digital and mixed level circuit and architecture design and validation](https://www.spintec.fr/wp-content/uploads/2023/03/logo_web-100x70.png)

Research. The hired person will join the spintronics IC design team, bringing complementary expertise in circuit design and architecture. The aim is to create a holistic chain of design and validation skills, covering all levels ...