Spin Orbit Torque Magnetic RAM (SOT-MRAM) approach represents a new way to overcome Spin Transfer Torque (STT) memory limitations by separating the reading and the writing paths.

It is particularly interesting for high-speed applications that do not require very high density because of two transistors per bit cell.

This work introduces a high-density SOT-MRAM memory based on a single transistor and a unidirectional diode.

The key idea to improve the area density of SOT-MRAM is to use one transistor per bit cell so that we can obtain a comparable density as DRAM and STT-MRAM

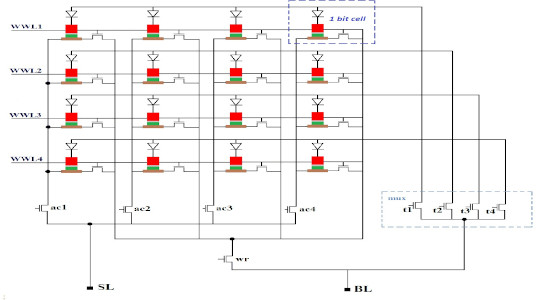

Figure 1 presents the architecture of 4×4 SOT-MRAM memory array based on a single transistor for writing and a unidirectional diode for reading.

The diode passes unidirectional current through MTJ during reading operation only, so zero leakage current is passing during write mode.

When a bit cell memory is selected in programming mode, all the transistors (ti) of multiplexer are kept deactivated. WWL1, write (wr), and access column (ac1) transistors are set to VDD to write the first cell.

Positive write voltage on BL (or SL) is applied so that the current is flowing from BL to SL through the conductive layer to write ‘1’ logic (or ‘0’).

On the other hand, when a memory cell is selected in reading mode, wr transistor and WWLi are kept low and the diode selector has to be polarized in forward mode to deliver the maximum current through the memory point.

Figure1. Equivalent schematic of 4×4 SOT-MRAM memory array based on a single transistor and one diode

Compared to conventional SOT-MRAM, which is based on two transistors, the area density is approximately improved by 20%.

For further density improvement, this diode can be developed by materials elements since minimizing the bit cell area is limited by the design rules.

For a matrix of order n rows and m columns, the number of transistors in our proposed architecture is m.(n+1) compared to conventional structure which is 2.(nxm) transistors.

Team: Spintronics IC design

Funding: CEA LETI, Minatec campus

Further reading: High density SOT-MRAM memory array based on a single transistor, 18th Non-Volatile Memory Technology Symposium (NVMTS), 2018. DOI: 10.1109/nvmts.2018.8603114

Contact: gregory.dipendina@cea.fr