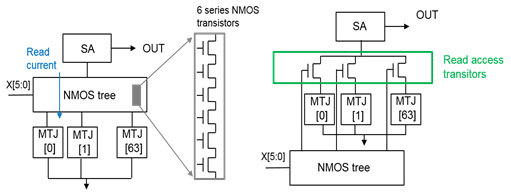

(left) General architecture of 6 inputs nvLUT where NMOS tree in series with MTJ. Read current passes through NMOS tree and MTJ selected flowing to the ground.

(right) Proposed architecture where NMOS tree and MTJ are separated. Read current passes through only one transistor and selected MTJ.

Continual growth in the size and functionality of FPGA over few years leads to an increasing interest in their use for high speed applications. However, the memory access speed limits the execution speed. The great amount of data affects the whole function. This work introduces a novel high speed and high-area efficiency MRAM based non-volatile Look-Up Table (nvLUT).

In opposition to ASIC, Application Specific Integrated Circuit optimized for a dedicated function, Field Programmable Gate Array (FPGA) is a key device to quickly realize prototyping systems. Their specifications and functions are directly programmable by users. Look-Up Table is the elementary cell of FPGA where data is usually stored into volatile memory cell, typically SRAM cells. Thanks to its non-volatility, the use of Magnetic Tunnel Junction (MTJ) could solve the power dissipation problem that is facing SRAM memories used for FPGA. It also makes the LUT much more energy efficient.

The number of input variables in LUT have a direct impact of the functional performance. In general, a larger number of inputs of the LUT is necessary because it gives the LUT the ability to realize and perform more complex logic functions. This leads also to a global area reduction. N-input LUT requires N-NMOS transistors connected serially. It forms this way a CMOS logic tree. Thus, during reading, high resistance becomes critical because the read current is limited due to series-NMOS transistors tree. Additionally, the propagation delay of output logic circuit is also dependent of inputs and becomes increasingly important when the number of inputs increases. The larger the number of inputs is, the slower the reading is. Finally, the number of input is limited because of functional reasons. To solve this set of issues, we proposed a new nvLUT architecture. It separates the CMOS logic tree from the reading path. Therefore, the propagation delay no more depends of the number of inputs and is constant. Thus, the reading current do not vary when the number of input variables in increased. It results a good delay of propagation whatever the nvLUT complexity.

In the case of an 8 input non-volatile Look-Up Table, our proposed circuit ensures a sufficient reading current. It offers a short delay whatever the number of inputs. This innovation offers a 55% sense delay reduction, 47% number of MTJ reduction, 46% power-delay product reduction. It also offer a wider possible input number. This architecture designed on a 130nm hybrid CMOS / MRAM process is presently under nano-fabrication. We expect to perform the tests in the coming months.

- Funding: CEA LETI, Minatec campus

- Further reading: High Speed and High-Area Efficiency Non-Volatile Look-Up Table Design Based on Magnetic Tunnel Junction, Rana Alhalabi, Gregory Di Pendina, Ioan-lucian Prejbeanu and Etienne Nowak, 17th Non-Volatile Memory Technology Symposium (NVMTS), 2017, DOI: 10.1109/NVMTS.2017.8171280

- Contact: Grégory Di Pendina.